XCV200-6FG456C FPGA: Jellemzők, specifikációk, programozás és alkalmazások

Az XCV200-6FG456C egy erőteljes FPGA (terepi programozható kapu tömb) az AMD Xilinx virtex® sorozatból.Ez az útmutató elmagyarázza annak tulajdonságait, a PIN -elrendezést, a programozási lépéseket és a felhasználásokat.A magas feldolgozási teljesítmény, a rugalmas tervezési lehetőségek és az erős bemeneti/kimeneti (I/O) képességekkel ez az FPGA segít a gyors és megbízható digitális rendszerek kiépítésében.Függetlenül attól, hogy hálózati, vezérlő rendszereken vagy egyedi elektronikán dolgozik, ez az útmutató segít megérteni, hogyan lehet az XCV200-6FG456C-t használni a projektekben.Katalógus

XCV200-6FG456C áttekintés

A Xcv200-6fg456c egy figyelemre méltó modell az AMD Xilinx Virtex® FPGA családban, amelynek célja, hogy robusztus programozható logikai megoldásokat biztosítson a komplex digitális rendszerek számára.Ez a specifikus chip körülbelül 236 666 rendszerkapit tartalmaz, és 1 176 konfigurálható logikai blokkot (CLB) és 5 292 logikai cellát tartalmaz.Ez magában foglalja az 57 344 összes RAM-bitet és támogatja a 284 I/O csapot, amelyet egy 456-golyó finom hangjelző gömbrácsos tömb (FBGA) csomagban helyeznek el, 23 mm x 23 mm-es méréssel.Ez a modell 2,5 V -os névleges feszültségen működik, 2,375 V -tól 2,625 V tartományban, és 0 ° C és 85 ° C hőmérsékleti tartományon belül működhet.A szélesebb Virtex® sorozat számos olyan alkalmazási tartományt kínál, amelynek sűrűségét 50 000 és több mint 1 millió rendszerkapu és a rendszerórát legfeljebb 200 MHz -ig terjeszti.Számos I/O szabványt támogat, beleértve többek között az LVTTL -t, az LVCMOS -t és a PCI -t.Az olyan funkciók, mint a késleltetett zárolt hurkok (DLL), a beágyazott memóriával rendelkező konfigurálható logikai blokkok és a aritmetikai műveletekhez szükséges dedikált hordozó logika javítják annak funkcionalitását.A Virtex® család garantálja a 0,22 um 5 rétegű fém eljárást, amely garantálja a teljesítményt és a megbízhatóságot.

Ha azt akarja, hogy integrálja a legmagasabb szintű FPGA technológiát a termékekbe vagy rendszerekbe, akkor az XCV200-6FG456C összegű vásárlása intelligens lépés.Ez megfelel az ipari előírásoknak, és fenntartja Önt a jövőbeli technológiai igények előtt.

Xcv200-6fg456c funkciók

• Rendszerkapu: Az XCV200-6FG456C körülbelül 236 666 rendszerkapárt kínál.Ez a magas kapuszám lehetővé teszi a komplex integrált digitális logikai áramkörök egyetlen chipen történő megvalósítását, javítva mind a teljesítményt, mind a sokoldalúságot számos alkalmazásban.

• Logikai források: Tartalmaz 1 176 konfigurálható logikai blokkot (CLB) és 5 292 logikai cellát.Ezek az erőforrások jót tesznek a rugalmas és méretezhető digitális áramkörök tervezéséhez.A CLB -k programozhatók a logikai funkciók széles skálájának végrehajtására, míg a nagyszámú logikai cella lehetővé teszi a kiterjedt logikai műveletek és folyamatok kezelését.

• Emlékezet: Az eszköz 57 344 bit RAM -ot biztosít, amelyet a logikai blokkjai között terjesztnek.Ezt a beágyazott RAM-ot olyan alkalmazásokhoz használják, amelyek gyors és hatékony adattárolást és visszakeresést igényelnek, támogatva a nagysebességű adatműveleteket a modern digitális rendszerekhez.

• I/O képességek: 284 bemeneti/kimeneti csapokkal az XCV200-6FG456C megkönnyíti a kiterjedt interfészi képességeket.Ezek az I/O csapok támogatják a különféle jelstandardokat, és lehetővé teszik az FPGA számára, hogy hatékonyan kommunikáljon a rendszer más alkatrészeivel, például memóriakészülékekkel, processzorokkal és perifériákkal.

• Feszültség és hőmérsékleti tartomány: 2,5 V névleges feszültséggel működik, elfogadható tartományban 2,375 V és 2,625 V között, ezt az FPGA-t alacsony teljesítményű fogyasztásra tervezték, miközben fenntartják a robusztus teljesítményt.0 ° C és 85 ° C közötti csatlakozási hőmérsékleti tartományon belül működhet, biztosítva a megbízhatóságot változó környezeti körülmények között.

XCV200-6FG456C PIN FUNKCIAM DIAGRAM

A XCV200-6FG456C PIN FUNKCIAM DIAGRAM az FPGA PIN -hozzárendeléseinek strukturált ábrázolása, amelyet különböző bankokba sorolnak be0. bank a 7. bankhoz).Mindegyik bankcsoport az FPGA csomagban történő funkciójuk és fizikai elhelyezésük alapján csap.A számozási és címkézési rendszer egy rácsmintát követ, ahol a sorokat betűkkel jelölik (A, B, C stb.), Az oszlopok számát (1, 2, 3 stb.), Amely megkönnyíti a specifikus csapok gyors azonosítását.Ezek a bankok megfelelnek a különböző bemeneti/kimeneti funkcióknak, az energiának, a földnek és a dedikált jelvezetésnek.A csapok különféle funkcionális csoportokat rendelnek, beleértve az általános célú I/O-t (GPIO), gyakran "G" (általános bemeneti/kimenet), "V" (feszültségellátás) és "O" (output) címkével.Az energia- és a földi csapok kifejezetten megjelölik, biztosítva a stabil FPGA működését.Különleges célú csapok, például az órás bemenetek, a visszaállítások és a vezérlőjelek olyan szimbólumokkal azonosítják, mint az "R" vagy a "T."Egyes csapok dedikált kommunikációs szerepeket is szolgálnak, ideértve a JTAG konfigurációt és a nagysebességű órákat is a programozáshoz és a hibakereséshez.

Xcv200-6fg456c blokkdiagram

Bemenet/kimeneti blokk

A diagram a Bemeneti/kimeneti blokk (IOB) Az XCV200-6FG456C FPGA szerkezete, amely a Xilinx Virtex család tagja.A diagram bemutatja a bemeneti és kimeneti műveletek során részt vevő kulcselemeket, kiemelve az adatáramlási és vezérlő mechanizmusokat.A diagram középpontjában három D flip-flopot használnak a jelek regisztrálására a bemeneti, kimenethez és a tri-state vezérléshez.A kimeneti nyilvántartást az OCE (kimeneti óra engedélyezése) jel vezérli, amely meghatározza a kimeneti adatok rögzítésének mikor.Hasonlóképpen, a Tri-State nyilvántartást a TCE (Tri-State óra engedélyezése) vezérli, lehetővé téve vagy letiltva a kimeneti puffert.A bemeneti regiszter rögzíti a bejövő adatokat, és programozható késleltetést alkalmaz, mielőtt átadja a belső FPGA logikához az IBUF -en keresztül (bemeneti puffer).Az OBUFT (Tri-State Output Buffer) biztosítja, hogy az FPGA vagy jelet vezessen a padra (I/O PIN), vagy pedig nagympedancia állapotba helyezze, a vezérlő logikától függően.A padon egy gyenge tartóáramkör tartozik az utolsó ismert logikai állapot fenntartása érdekében, ha nincs aktív vezető, megakadályozva a nem szándékos lebegő körülményeket.A referenciafeszültséget (VREF) bizonyos bemeneti standardokhoz, például SSTL -hez vagy HSTL -hez használják, amelyek pontos feszültségszintet igényelnek a megfelelő működéshez.Összességében ez az IOB-struktúra lehetővé teszi az FPGA számára, hogy kezelje a nagysebességű adatátvitelt, támogassa a különböző I/O szabványokat, és rugalmas irányítást biztosítson a jel időzítése és integritás felett.

Mester/rabszolga soros mód

A Mester/rabszolga soros mód A blokkdiagram szemlélteti a Virtex FPGA, különösen az XCV200-6FG456C konfigurációs folyamatát, amikor egy daisy-láncú konfigurációba programozva soros EEPROM (XC1701L) programozva van.Ebben a beállításban az egyik Virtex eszköz mesterként működik, a konfigurációs órát (CCLK) vezérli, és a konfigurációs adatokat sorozatosan továbbítja a lánc további rabszolga FPGA -jához.A Master FPGA kezdeményezi a konfigurációs folyamatot a programjel érvényesítésével, a lánc összes eszközének visszaállításával.Miután az inicializálás befejeződött, az init jel jelzi a készséget, és a konfigurációs adatok a soros EEPROM -ból (XC1701L) az FPGA Master PIN (adatai) PIN -kódjába kerülnek.A Master FPGA elolvassa az EEPROM -ból származó adatokat, és továbbítja azt a Dout (Data Out) révén a későbbi rabszolga FPGA -khoz, szinkronizálva az adatátvitelt a CCLK jel segítségével.A kész jelet a sikeres konfiguráció jelzésére használják, opcionális pull-up ellenállással, amely biztosítja a stabil magas állapotot, amikor a konfiguráció befejeződik.Az XC1701L EEPROM -ot a Master FPGA vezérli a CLK, Data, CE (chip Enable) és a reset/OE (kimeneti engedélyezési) jelek segítségével, biztosítva, hogy a tárolt konfigurációs adatok helyesen kerüljenek le.Ez a konfigurációs módszer hatékony a több FPGA programozásához egyetlen EEPROM alkalmazásával, csökkentve a külső vezetékek bonyolultságát és biztosítva, hogy minden eszköz szinkronizált konfigurációs adatokat fogadjon.

XCV200-6FG456C specifikációk

|

Beír |

Paraméter |

|

Gyártó |

Amd xilinx

|

|

Sorozat |

Virtex® |

|

Csomagolás |

Tálca |

|

Alkatrész állapota |

Elavult |

|

Labs/CLB -k száma |

1176 |

|

A logikai elemek/cellák száma |

5292 |

|

Összes RAM BITS |

57344 |

|

I/O száma |

284 |

|

A kapuk száma |

236666 |

|

Feszültség - ellátás |

2,375V ~ 2,625 V |

|

Szerkesztési típus |

Felszíni |

|

Üzemi hőmérséklet |

0 ° C ~ 85 ° C (TJ) |

|

Csomag / tok |

456-BBGA |

|

Beszállító eszköz csomag |

456-FBGA (23x23) |

|

Alaptermék száma |

XCV200 |

XCV200-6FG456C alkalmazások

Távközlés és hálózatépítés

Az XCV200-6FG456C kiemelkedik a telekommunikációban és a hálózatépítési alkalmazásokban, mivel képes kezelni a nagysebességű adatátvitelt és az összetett jelfeldolgozási feladatot.Magas kapuszáma és robusztus I/O képességei lehetővé teszik, hogy támogassa a funkciókat, például a csomagfeldolgozást, a jelmodulációt/demodulációt és a hibajavító protokollokat.

Digitális jelfeldolgozás (DSP)

Ideális a DSP alkalmazásokhoz, ez az FPGA gyors és összetett matematikai számításokat végezhet az audio- és videofeldolgozási technológiákban.Legyen szó multimédiás rendszerekről, hangfelismerésről vagy streaming szolgáltatásokról, az XCV200-6FG456C nagy teljesítményű feldolgozási képességei, valamint a beágyazott memória-támogatás hatékony és jó minőségű jelfeldolgozása.

Ipari vezérlőrendszerek

Az ipari automatizálás során az XCV200-6FG456C biztosítja a szükséges teljesítményt a vezérlőrendszerek és az automatizálási hálózatok kezeléséhez.Képessége, hogy egyszerre hajtson végre több vezérlési feladatot, miközben biztosítja a válaszidőket, alkalmassá teszi a folyamatvezérlés, a robotika és a gépi látás alkalmazásait.

Orvosi műszerek

Az FPGA pontossága és sebessége nagyszerű az orvosi képalkotó és diagnosztikai berendezésekben, ahol elősegíti a komplex algoritmusok feldolgozását olyan képalkotó alkalmazásokhoz, mint az MRI, az ultrahang és a CT szkennelés.Az XCV200-6FG456C képességei biztosítják, hogy képes kezelni a modern orvosi technológiában szükséges magas adatátviteli sebességet és bonyolult feldolgozást.

Xcv200-6fg456c hasonló alkatrészek

XCV200-6FG456C programozási lépések

Programozási lépések az XCV200-6FG456C-hez:

1. Tervezési bejegyzés

Az FPGA programozás kezdeti fázisa magában foglalja a rendszer digitális logikájának és funkcionalitásának meghatározását.Ezt meg lehet tenni a hardverleírási nyelvek (HDLS), például a VHDL vagy a Verilog használatával, ahol olyan kódot ír, amely meghatározza, hogy az FPGA hogyan dolgozza fel az adatokat, és kölcsönhatásba lép más hardverekkel.Az FPGA tervező szoftverekben, például a Xilinx ISE -ben vagy a Vivado -ban elérhető vázlatos belépési eszközök felhasználhatók.Ez a módszer magában foglalja a logika vizuális ábrázolásának létrehozását az összetevők húzásával és eldobásával, amelyek egyesek intuitívabbak, mint a kód írása.

2. Szintézis

Miután a formatervezés befejeződött, a következő lépés a szintézis, ahol egy olyan eszköz, mint a Xilinx XST (Xilinx Synthesis Technology), átalakítja a HDL -kódot vagy a vázlatos kialakítást hálózati listává.Ez a hálózati lista az áramkört az általános digitális alkatrészek, például a logikai kapuk és a regiszterek szempontjából írja le.A szintézis folyamat magában foglalja a tervezés optimalizálását is a teljesítménykövetelmények teljesítése és az erőforrás -felhasználás minimalizálása érdekében az FPGA hatékony működéséhez.

3. Végrehajtás

A megvalósítási folyamat a fordítással kezdődik, a tervezés kombinálásával olyan kényszerfájlokkal, amelyek olyan paramétereket határoznak meg, mint például az óra frekvenciái és a PIN -hozzárendelések.A fordítást követően a leképezési szakasz a hálózati listájának elemeit az FPGA speciális fizikai erőforrásaihoz, például a keresési táblákhoz (LUTS) és a papucshoz rendeli.Az elhelyezés és az útválasztási szakasz ezután meghatározza az egyes komponensek fizikai elhelyezkedését az FPGA architektúráján belül, és a programozható összekapcsolási erőforrások révén meghatározza a kapcsolatokat.Ez a szakasz kiválóan alkalmas a kívánt teljesítménymutatók elérésére, beleértve az órafrekvenciákat is.

4. Bitstream generáció

A sikeres elhelyezés és útválasztás után az eszköz bitstream, egy bináris konfigurációs fájlt generál, amely tartalmazza az FPGA összes programozási információt.Gyakran ajánlott a végső tervezés utáni elhelyezés szimulálása annak biztosítása érdekében, hogy a bitstream körülmények között a várt módon viselkedjen.Ez az ellenőrzési lépés segít elkerülni a lehetséges problémákat a tényleges működés során.

5. Konfiguráció

Az utolsó lépés magában foglalja a bitream betöltését az FPGA -ba, különféle konfigurációs módszerekkel.A Slave-Serial Mode, egy egyszerű és költséghatékony opció, az FPGA-t egy külső mester eszközön keresztül konfigurálja, amely sorosan továbbítja az adatokat.Mester-sorozatú módban az FPGA önállóan olvassa el a bitream-t egy csatolt soros promóciótól.A nagysebességű konfigurációkhoz a SelectMap mód lehetővé teszi a külső mikroprocesszor számára, hogy az adatokat gyorsan betöltse az FPGA-ba.Ezenkívül a JTAG módot nemcsak a programozáshoz, hanem a teszteléshez és a hibakereséshez is használják, a rendszeren belüli programozáshoz és a határ-szkennelés teszteléséhez.

XCV200-6FG456C előnyök

Teljesítmény

A Xilinx virtex sorozatot, amelyhez az XCV200-6FG456C tartozik, a nagysebességű teljesítményhez optimalizálva van, és 200 MHz-es rendszer óráit kínálja.Ez lehetővé teszi a gyors adatfeldolgozást igénylő alkalmazásokhoz, biztosítva a komplex algoritmusok és a nagysebességű műveletek, például a telekommunikáció, a feldolgozás és a multimédia hatékony kezelését.

I/O szabványok támogatása

Ez az FPGA a bemeneti/kimeneti szabványok széles skáláját támogatja, beleértve az LVTTL, LVCMOS, PCI, GTL, HSTL, SSTL, CTT és AGP.Az ilyen kiterjedt I/O szabványok támogatása lehetővé teszi az XCV200-6FG456C számára, hogy zökkenőmentesen integrálódjon a különféle rendszerkomponensekbe, javítva hasznosságát a különféle digitális ökoszisztémák között.Ez a rugalmasság lehetővé teszi az FPGA alkalmazkodását a különböző interfészi feltételekhez, a rendszer módosítása nélkül.

Órakezelés

Az XCV200-6FG456C többszörös késleltetett hurkokat (DLL) tartalmaz az óra eloszlásához és kezeléséhez a rendszeren belül.Ezek a DLL -ek elősegítik a rendszer időzítésének és megbízhatóságának javítását azáltal, hogy pontos órás jeleket biztosítanak a szinkron műveletekhez.Ez a szolgáltatás fontos a rendszerhibák csökkentésében és az általános teljesítmény javításában, különösen az összetett tervekben, amelyek pontos időzítést és szinkronizálást igényelnek.

Tervezési rugalmasság

Az XCV200-6FG456C 1,176 konfigurálható logikai blokkkal és 5 292 logikai cellával jelentős logikai erőforrásokat kínál, amelyek képesek a funkciók változatos tartományának megvalósítására.Az egyszerű ragasztó logikától a bonyolult digitális rendszerekig ez az FPGA támogatja a komplex tervezési követelményeket, ideálisvá téve az egyedi számítástechnika, a digitális jelfeldolgozás és a prototípus készítése során alkalmazott alkalmazásokhoz.

Gyors prototípus készítése

Az olyan FPGA-k, mint az XCV200-6FG456C, híresek a gyors prototípusok támogatására.Ez az eszköz lehetővé teszi a gyors tervezési iterációkat, és újrakonfigurálható a helyszínen, ami előnye a fejlesztési ciklusoknak, mivel csökkenti a piacra dobott időt.Hatékonyan alkalmazkodik a projekt specifikációinak követelményeinek vagy frissítéseinek megváltoztatásához, biztosítva, hogy a végső termékek naprakészek legyenek a legújabb technológiai szabványokkal.

Integrációs képesség

Az XCV200-6FG456C integrációs képességei megkönnyítik a több diszkrét alkatrész konszolidációját egyetlen chipré.Ez az integráció csökkentheti a rendszer komplexitását, az alacsonyabb energiafogyasztást és a költségmegtakarítást.A szükséges különálló alkatrészek számának minimalizálásával ez az FPGA leegyszerűsíti a tervezési folyamatokat, és javítja az általános rendszer megbízhatóságát és tömörségét.

XCV200-6FG456C csomagolási méretek

Az XCV200-6FG456C egy Field programozható kapu tömb (FPGA) az AMD Virtex® sorozatából, amely egy 456-golyó finom-pitch golyósrács tömb (FBGA) csomagban található.

• Csomagtípus: 456-FBGA

• Csomagméret: 23 mm x 23 mm

• Golyóhely: 1,0 mm

XCV200-6FG456C gyártó

Az XCV200-6FG456C egy terepi programozható kapu tömb (FPGA), amelyet eredetileg a Xilinx fejlesztett ki, amely a nagy teljesítményű programozható logikai eszközökről ismert.A Xilinx megszerzése után AMD, az XCV200-6FG456C most az AMD-vel társul, mint jelenlegi gyártó.Ez az FPGA modell azonban elavult és már nem a termelésben.Az AMD továbbra is támogatja az újabb FPGA architektúrákat, amelyek fokozott teljesítmény, energiahatékonyság és hosszabb élettartamúak, így a modern alternatívák előnyösek az új terveknél.

Következtetés

Az XCV200-6FG456C sokoldalú és nagysebességű FPGA, sok technológiai alkalmazás számára hasznos.Miközben már nem készül, ez még mindig jó választás azoknak a régebbi rendszereknek, amelyek megbízható teljesítményt igényelnek.Ez az útmutató lefedte a tervezési, programozási lépéseket és a gyakorlati felhasználásokat, megkönnyítve annak megértését, hogyan működik, és hogyan lehet felhasználni.Ahogy az újabb FPGA -k elérhetővé válnak, felhasználhatja ezt a tudást az Ön igényeinek megfelelő FPGA kiválasztására és a digitális tervek javításához.

Adatlap PDF

XCV200-6FG456C adatlapok:

Rólunk

ALLELCO LIMITED

Olvass tovább

Gyors lekérdezés

Kérjük, küldjön egy kérdést, azonnal válaszolunk.

Gyakran Ismételt Kérdések [FAQ]

1. Mekkora az XCV200-6FG456C energiafogyasztása?

Az XCV200-6FG456C 2,5 V-on működik, feszültségtartományban 2,375 V-2,625 V.Az energiafogyasztás a logika felhasználásától és az óra gyakoriságától függ, de régebbi FPGA-ként ez kevésbé hatékonyságú, mint az újabb Xilinx-eszközök.Meg kell fontolni a megfelelő energiagazdálkodást és a hőeloszlást.

2. Hogyan hasonlítja össze az XCV200-6FG456C az XCV200-6FG256C-vel?

Az XCV200-6FG456C nagyobb csomaggal (456-golyó FBGA) van, összehasonlítva az XCV200-6FG256C-vel (256-golyó FBGA), amely több I/O csapot kínál (284 vs. 172), és potenciálisan jobb teljesítményt nyújt a kiterjedt interfészeléshez szükséges alkalmazásokhoz.Ha a tervezés több I/O képességre támaszkodik, akkor az XCV200-6FG456C a jobb választás.

3. Átprogramozhatom az XCV200-6FG456C-t többször?

Igen, az XCV200-6FG456C egy SRAM-alapú FPGA, azaz korlátlanul átprogramozható, amennyire a hatalom biztosítása van.Ugyanakkor szükség lesz külső nem felejtő memóriára (EEPROM vagy Flash), hogy megtartsa a bittream-t egy energiaciklus után.

4. Az XCV200-6FG456C támogatja-e a nagysebességű soros kommunikációt?

Az XCV200-6FG456C több I/O szabványt, például LVTTL, LVCMOS, PCI, GTL, HSTL és SSTL-t támogat, de nem rendelkezik beépített nagysebességű SERDES-vel (Serializer/Deserializer) vagy Transceiver, mint a modern FPGA-k.A nagysebességű soros linkeket igénylő alkalmazásokhoz (például PCIe, Gigabit Ethernet vagy HDMI) vegye figyelembe az újabb FPGA modelleket.

5. Hogyan hasonlít az XCV200-6FG456C az újabb FPGA modellekhez?

Az XCV200-6FG456C az FPGA-k idősebb generációjához tartozik.A modern Virtex FPGA -khoz képest alacsonyabb kapuszám, lassabb órasebesség és korlátozott energiahatékonysággal rendelkezik.Az újabb modellek magasabb logikai sűrűségű, beágyazott memóriát, fejlett DSP blokkokat és alacsonyabb energiafogyasztást kínálnak, ami jobbá teszi őket a modern alkalmazásokhoz.

Az AD73322AR pinout, a funkciók és a műszaki részletek magyarázata

2025/03/21 -en

EP20K100EFC324-1X FPGA: Jellemzők, specifikációk, alkalmazások és programozási útmutató

2025/03/20 -en

Népszerű hozzászólások

-

Komplex utasítás beállított számítógépek: Hogyan változtatták meg a számítástechnikát?

8000/04/18 -en 147760

-

USB-C pinout és funkciók

2000/04/18 -en 111974

-

A Xilinx Unified Simulation Primitívumok használata: Átfogó útmutató az FPGA tervezéséhez és szimulációjához

1600/04/18 -en 111351

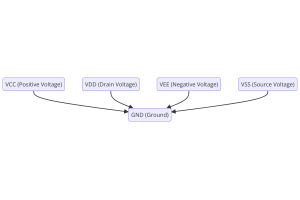

-

Tápfeszültségek az elektronikában: VCC, VDD, VEE, VSS és GND jelentése

0400/04/18 -en 83742

-

RJ45 Csatlakozó útmutató: Pinout, vezetékek, kábeltípusok és felhasználások

1970/01/1 -en 79527

-

A végső útmutató a vezetékes színkódokhoz a modern elektromos rendszerekben

Az, ahogyan az elektromos rendszereink a színeket használják, nem csak a megjelenéshez.Minden huzalszín most egy adott funkciót jelöl, megkönnyítve az elektromos alkatrészek azonosítását és kezelés...1970/01/1 -en 66936

-

Tisztító szelep útmutató: funkció, tünetek, tesztelés és a motor optimális teljesítményének cseréje

A tisztítószelep az autó rendszerének kulcsfontosságú része, amely segít a levegő tisztaságának megőrzésében az üzemanyag -gőzök kezelésével, mielőtt elmenekülhetnek a légkörbe.Ez nem csak a szenny...1970/01/1 -en 63086

-

Minőség (q) tényező: egyenletek és alkalmazások

A minőségi tényező, vagy a „Q” fontos, amikor ellenőrzi, hogy az induktorok és a rezonátorok hogyan működnek az elektronikus rendszerekben, amelyek rádiófrekvenciákat (RF) használnak.A 'Q' megméri,...1970/01/1 -en 63025

-

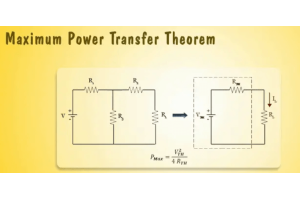

A csúcsteljesítmény elérése a maximális energiaátviteli tételgel

A maximális teljesítményátviteli tétel elmagyarázza, hogy a forrásból, például az akkumulátorból vagy a generátorból származó energia hogyan áramlik a csatlakoztatott terhelésbe.Megmutatja azt a po...1970/01/1 -en 54092

-

A23 akkumulátor specifikációi és kompatibilitása

Az A23 akkumulátor egy kicsi, hengeres alakú akkumulátor, nagy feszültséggel.A 23A, 23AE vagy MN21 néven is 12 voltos és sokkal magasabb, mint az AA vagy AAA akkumulátorok.Különleges kiala...1970/01/1 -en 52167