Lattice LFEC3E-3QN208C FPGA útmutató: Jellemzők, adatlap és alternatívák

Ha olyan projekteken dolgozik, amelyek megbízható logikai ellenőrzést igényelnek anélkül, hogy túllépnék a költségvetést, akkor érdemes megismerni az LFEC3E-3QN208C FPGA-t.Ez biztosítja a logika, a memória és az I/O rugalmasság megfelelő keverékét egy kompakt csomagban.Ebben az útmutatóban látni fogja annak fő tulajdonságait, hogyan működik benne, hol használhatja, hogyan programozhatja, és milyen előnyöket és korlátokat várhat el.Katalógus

Mi az LFEC3E-3QN208C?

A LFEC3E-3QN208C A Lattice Semiconductor EC/ECP családjának FPGA eszköze, amelyet a vállalat gazdasági osztályú programozható logikai sorozatának részeként terveztek.A költséghatékonyság és a megbízható teljesítmény egyensúlyának kiegyensúlyozása érdekében ez az eszköz skálázható architektúrát kínál a digitális logika megvalósításához.A „QN208C” utótag azonosítja a Compact 208-PIN csomagját, így az integrációhoz alkalmas, ahol a tábla tere aggodalomra ad okot.Az érett Latticeec/ECP család tagjaként hordozza a rugalmasság és a terméksorban található megbízható formatervezés jellemzőit.

LFEC3E-3QN208C-t keres?Vegye fel velünk a kapcsolatot, hogy ellenőrizze az aktuális készleteket, az átfutási időt és az árakat.

LFEC3E-3QN208C szolgáltatások

• Logikai kapacitás

Az LFEC3E-3QN208C mintegy 3100 logikai elemet biztosít, amelyek felhasználhatók digitális áramkörök, állami gépek és egyedi adatapaták megvalósítására.Ez a sűrűség olyan középtávú tervekhez, mint a kommunikációs interfészek, az ipari vezérlés és a beágyazott feldolgozás, alkalmas.

• Chip memória

Körülbelül 56 320 bites blokk RAM -ot és elosztott RAM -ot integrál, lehetővé téve az adatpufferek, a keresési táblák vagy a kis FIFO -k tárolását közvetlenül az FPGA belsejében.Ez csökkenti a külső memória iránti támaszkodást számos közepes méretű adatfeladat esetén.

• I/O források

A 208 pólusú QFP csomagban található eszköz a konfigurációtól függően mintegy 140 felhasználói I/O csapot támogat.Ez rugalmasvá teszi a több interfész, párhuzamos busz vagy vegyes jel összeköttetést igénylő alkalmazások számára.

• Üzemi feszültség

A mag körülbelül 1,2 V-nél működik, az I/O bankok 1,2 V-tól 3,3 V-ig tartó több feszültség-standardot támogatnak. Ez a széles kompatibilitás lehetővé teszi az FPGA számára, hogy összekapcsolódjon mind a modern alacsony feszültségű logikával, mind a Legacy 3.3 V rendszerekkel.

• Rendszer -óra

Az eszköz magában foglalja a CHIP PLL-eket (SYSCLOCK ™), amelyek szaporodhatnak, megoszthatnak vagy fáziseltolódási bemeneti órákat.Ez lehetővé teszi a DDR interfészek, a nagysebességű adatútok és a szinkronizált logikai tartományok pontos belső óráinak előállítását.

• Memória interfész támogatás

Az LFEC3E-3QN208C támogatja a DDR SDRAM interfészeket a DDR-400-ig (200 MHz-es óra).Ez lehetővé teszi, hogy közvetlenül csatlakozzon a külső memória chipekhez a magasabb kapacitású tároláshoz vagy pufferáláshoz az adatintenzív alkalmazásokban.

• I/O szabványok

Támogatja az ipari szabványos jelátviteli protokollokat, beleértve az LVCMOS-t, az LVTTL, az SSTL, a HSTL, a PCI és az LVD-ket.Ez biztosítja a kompatibilitást a processzorok széles körével, az ASIC -kkel és a kommunikációs interfészekkel.

• Rendszeren belüli programozhatóság

Az FPGA programozható a JTAG-n keresztül (IEEE 1149.1), és támogatja a rendszeren belüli újrakonfigurációt.Ez egyértelművé teszi a fejlesztés, a hibakeresési és a terepi frissítéseket anélkül, hogy eltávolítaná az eszközt a PCB -ből.

• Hibakeresés és elemzés

Támogatást nyújt a Lattice ISPTracy Logic Analyzeréhez, amely időben a belső jeleket vizsgálja.Ez a szolgáltatás egyszerűsíti a komplex logikai tervek hibakeresését, anélkül, hogy külső szondákra lenne szükség.

• Életciklus állapota

Az LFEC3E-3QN208C a rácsos EC családhoz tartozik, amelyet ma érett vagy megszűnt termékcsaládnak tekintnek.

Latticeec blokkdiagram

A Latticeec FPGA család blokkdiagramja (mint például az LFEC3E-3QN208C) megmutatja, hogy a belső architektúrát hogyan szervezik a logika, a memória és az összeköttetés egyensúlyához.A szélek körül programozható I/O cellák (PICS), amelyek a külső eszközökkel folytatott kommunikációt kezelik, és több feszültségszabványt támogatnak a rugalmas interfészekhez.Belül a rács tele van programozható funkcionális egységekkel (PFU), ahol a felhasználói logika megvalósul, míg a dedikált Sysmem beágyazott blokk RAM-ok (EBR) nagysebességű memóriát biztosítanak a pufferoláshoz és az adattároláshoz.A rendszer erőforrásai közé tartozik a Sysclock PLL-ek, amelyek kezelik az óratermelést és a szinkronizálást, a stabil nagyteljesítményű működést és a SYSConfig/JTAG portokat, amelyek lehetővé teszik a rendszeren belüli programozást és tesztelést.Ez az elrendezés az FPGA sokoldalúvá teszi az újrakonfigurálható logikát, a beágyazott memóriát és a robusztus I/O -t a kommunikáció, a vezérlés és a beágyazott rendszerek széles skálájához.

Latticeec Banks diagram

A Latticeec Banks-diagram olyan eszközökre, mint például az LFEC3E-3QN208C, szemlélteti, hogy az FPGA I/O csapjainak hogyan vannak felépítve nyolc bankba, mindegyiknek saját ellátási és referenciakormányával.Minden bank önállóan hajtható meg a V -n keresztülCCIO A csapok, amelyek lehetővé teszik az FPGA számára, hogy több I/O feszültségszabványt (például 1,2 V, 1,8 V, 2,5 V vagy 3,3 V) támogasson.Minden bank tartalmazza a V -t isRef. A csapok, amelyek kiválóan alkalmasak bizonyos szabványokhoz, például az SSTL -hez és a HSTL -hez, amelyek referenciafeszültségeket igényelnek a megfelelő logikai küszöbök beállításához.Ez a moduláris struktúra rugalmasságot biztosít az FPGA különböző külső komponensekkel, például processzorokkal, memóriával és perifériákkal történő interfészhez.A bankos architektúra javítja a termék sokoldalúságát, és megkönnyíti a vegyes feszültségrendszerekbe történő integrációját, ami az ipari és kommunikációs alkalmazások kulcsfontosságú előnye.

LFEC3E-3QN208C specifikációk

|

Beír |

Paraméter |

|

Gyártó |

Rácsos félvezető társaság |

|

Sorozat |

EK |

|

Csomagolás |

Tálca |

|

Alkatrész állapota |

Elavult |

|

A logikai elemek/cellák száma |

3100 |

|

Összes RAM BITS |

56,320 |

|

I/O száma |

145 |

|

Feszültség - ellátás |

1,14v ~ 1,26 V |

|

Szerkesztési típus |

Felszíni |

|

Üzemi hőmérséklet |

0 ° C ~ 85 ° C (TJ) |

|

Csomag / tok |

208-bfqfp |

|

Beszállító eszköz csomag |

208-PQFP (28 × 28) |

|

Alaptermék száma |

Lfec3 |

LFEC3E-3QN208C alkalmazások

1. beágyazott vezérlőrendszerek

Az LFEC3E-3QN208C az ipari automatizálás, robotika vagy motorvezérlő rendszerek központi logikai vezérlőjeként szolgálhat.Az átprogramozó architektúrája lehetővé teszi az egyedi állami gépek és az időmérés-kritikus logika megvalósítását a hardver újratervezése nélkül.Alacsony magfeszültséggel és több I/O bankkal zökkenőmentesen integrálódik mind a modern érzékelőkhöz, mind a hagyományos vezérlőkhöz.Ez ideálissá teszi a megbízható, időbe beágyazott vezérlési megoldásokhoz.

2.

Mivel az FPGA támogatja a több I/O szabványt és a feszültségszintet, hídként szolgálhat a különböző kommunikációs protokollok között.Például lefordíthat a régi buszok (például a PCI vagy a párhuzamos interfészek) és az újabb szabványok, például az LVD vagy a DDR memória között.Ez a képesség elősegíti a meglévő rendszerek élettartamát, miközben lehetővé teszi az új eszközök integrációját.Ez a rugalmasság csökkenti a külső ragasztó logika szükségességét és felgyorsítja a rendszer integrációját.

3. jelfeldolgozás a kommunikációban

Az LFEC3E-3QN208C képes kezelni az alapvető DSP-feladatokat, ideértve a szűrést, a hibakutatást vagy a csomagkezelést a kommunikációs rendszerekben.Beágyazott blokk RAM és logikai cellák hatékony erőforrásokat biztosítanak az adatfolyamok pufferálásához és kezeléséhez.Ha ezeket a funkciókat egy mikroprocesszorból kiszállítja, az általános rendszer -átviteli sebesség és a reagálhatóság javul.Ez lehetővé teszi vezeték nélküli modulokhoz, kisméretű alapállomásokhoz és hálózati berendezésekhez.

4. teszt, mérés és műszerezés

A teszt- és mérőberendezésekben, például oszcilloszkópokban, adatnaplókban vagy logikai analizerekben az FPGA konfigurálható az adatok időben történő rögzítésére, szűrésére és előfeldolgozására.Programozható I/O bankjai lehetővé teszik a közvetlen kapcsolatot a különböző jelszintekhez extra konverziós áramkör nélkül.A beágyazott RAM kihasználásával az ideiglenes adatok hatékonyan tárolhatók és továbbíthatók a külső processzoroknak.Ez a képesség javítja a pontosságot és csökkenti a késést a műszerezés alkalmazásaiban.

5. Prototípus készítése és egyedi hardvergyorsítók

Az eszköz platformként szolgálhat a hardver prototípus készítéséhez vagy a kis léptékű gyorsítókhoz.A titkosítási blokkokat, az ellenőrző összegű generátorokat vagy más számítási igényes feladatokat közvetlenül a logikában valósíthatja meg.Ez lerövidíti a fejlesztési ciklust az ASIC -khez képest, és lehetővé teszi a gyors módosításokat a terepen.Kutatáshoz, induló vállalkozásokhoz és egyedi beágyazott megoldásokhoz költséghatékony belépési pontot kínál az FPGA-alapú gyorsuláshoz.

LFEC3E-3QN208C Hasonló alkatrészek

|

Meghatározás |

LFEC3E-3QN208C |

LFEC3E-3QN208I |

LFEC3E-3Q208I |

LFEC3E-3TN100C |

LFEC3E-3TN144C |

LFEC3E-3FN256C |

|

Logikai elemek / cellák |

3100 |

3100 |

3100 |

3100 |

3100 |

3100 |

|

Beágyazott memória (bitek) |

56,320 |

56,320 |

56,320 |

56,320 |

56,320 |

56,320 |

|

Maximális működési frekvencia |

~ 340 MHz |

~ 340 MHz |

~ 340 MHz |

~ 340 MHz |

340 MHz |

340 MHz |

|

I/OS száma |

145 |

145 |

145 |

~ 80–90 |

97 |

160 |

|

Alapfeszültség -tartomány |

1,14 V - 1,26 V |

1,14 V - 1,26 V |

1,14 V - 1,26 V |

1,14 V - 1,26 V |

1,14 V - 1,26 V |

1,14 V - 1,26 V |

|

Üzemi hőmérséklet |

0 ° C - 85 ° C |

0 ° C - 85 ° C |

0 ° C - 85 ° C |

0 ° C - 85 ° C |

0 ° C - 70 ° C |

0 ° C - 85 ° C |

|

Csomagtípus |

208 PIN QFP |

208 PIN QFP |

208 PIN QFP |

100 tűs TQFP |

144 pólusú TQFP |

256-ball BGA |

|

Életciklus állapota |

Elavult |

Elavult |

Elavult |

Elavult |

Elavult |

Elavult |

|

I/O szabványok támogatottak |

LVCMOS, LVTTL, LVDS, SSTL, HSTL, PCI |

Azonos |

Azonos |

Limited (kevesebb bank) |

Ugyanaz a készlet, kevesebb csap |

Teljes készlet több bankkal |

|

Külső memória -támogatás |

DDR a DDR-400-ig |

DDR a DDR-400-ig |

DDR a DDR-400-ig |

DDR a DDR-400-ig |

DDR a DDR-400-ig |

DDR a DDR-400-ig |

LFEC3E-3QN208C programozási lépések

Mielőtt használhatja az LFEC3E-3QN208C FPGA-t, be kell programoznia az egyedi kialakítással.A folyamat magában foglalja a logikai kialakítás létrehozását, a bitream előállítását és a chipbe történő átvitelét a támogatott interfészeken keresztül.

1. Tervezés és bitstream generáció

Először úgy kezdi, hogy a tervezést HDL -ben (Verilog vagy VHDL) írja, majd összeállítja azt rácsos fejlesztési eszközökkel, mint például az Isplever vagy a Diamond.E folyamat során szintetizálja a logikát, elvégzi az elhelyezést és az útválasztást, és alkalmazza az I/O -t és az időzítési korlátokat.Az eszköz ezután bitstream fájlt (.bit vagy .jed) készít, amely tartalmazza az FPGA által megkövetelt összes konfigurációs adatot.Ezt a fájlt az az, amit később áthelyez az eszközbe, hogy életre keltse a tervét.

2. Válassza ki a konfigurációs módot

Ezután el kell döntenie, hogy az FPGA hogyan tölti be a konfigurációját.Az LFEC3E-3QN208C több üzemmódot támogat, például a JTAG programozás közvetlen letöltéshez vagy a SYSConfig módokhoz, például a Serial vagy Parally Boot-ról a külső flash memóriából.Az üzemmódot úgy választja ki, hogy beállítja az eszköz konfigurációs csapjait (CFG [2: 0]), vagy a külső memória megfelelő vezetékkel.A megfelelő mód kiválasztása attól függ, hogy gyors prototípus-készítést vagy állandó, bekapcsolási konfigurációt szeretne-e.

3. Csatlakoztassa a programozási felületet

A mód kiválasztása után csatlakoztatja a megfelelő programozási hardveret.A JTAG -hoz letöltési kábelt vagy programozót fog használni, amely az FPGA JTAG csapjaihoz kapcsolódik.Ha a SysConfig -ot használja, akkor egy külső vaku vagy mikrovezérlő lesz konfigurációs forrásként.A megfelelő huzalozás, a PIN -hozzárendelések és az energia -szekvenálás biztosítása ebben a szakaszban jó a megbízható programozáshoz.

4. Töltse be a konfigurációt

Ha a hardver a helyén van, akkor a bitstream -t átvitte az FPGA -ba.A programozó az adatokat a JTAG vagy a SYSConfig felületen keresztül küldi el, és az FPGA a belső konfigurációs memóriájába írja.E folyamat során az eszköz ellenőrzi az adatok integritását a CRC segítségével, és a SIGKS SICKE SICKE -t állítja elő, hogy a Kész PIN -kódot magasra állítja.Ezen a ponton a formatervezés aktívvá válik, és az FPGA elkezdi működni, amikor programozta.

5. Futási idő és újrakonfiguráció

Végül lehetősége van arra, hogy újrakonfigurálja az eszközt anélkül, hogy eltávolítaná a rendszerből.A JTAG vagy a SYSConfig használatával újra frissítheti az FPGA -t egy új bitstream segítségével, ha a tervezés megváltozik.Ez a képesség hasznos a terepi frissítésekhez vagy az iteratív teszteléshez.A rendszeren belüli programozhatóság kihasználásával biztosítja, hogy az LFEC3E-3QN208C idővel alkalmazkodjon a változó követelményekhez.

LFEC3E-3QN208C előnyök és hátrányok

Előnyök

• Olcsó FPGA opció költségvetés-érzékeny mintákhoz

• Alacsony energiafogyasztás sok alternatívához képest

• Kiegyensúlyozott erőforrások túltervezés nélkül

• Erős örökölt ökoszisztéma és bizonyított megbízhatóság

• Rugalmas konfiguráció JTAG vagy SYSConfig módokon keresztül

Hátrányok

• Alacsonyabb teljesítménymennyezet, mint a csúcskategóriás FPGA-k

• Korlátozott logikai sűrűség és memóriakapacitás

• Az elavulás kockázata egy érett/megszüntetett vonal részeként

• Hiányzik a fejlett funkciók, például a DSP blokkok vagy a SERDES

• Teljesítmény/teljesítmény kompromisszumok magasabb felhasználáskor

LFEC3E-3QN208C csomagolási méretek

|

Beír |

Paraméter |

|

Csomagtípus |

208-PQFP (műanyag quad lapos csomag) |

|

Testméret (l × w) |

28 mm × 28 mm |

|

Csomagmagasság (max) |

3,40 mm |

|

Hangmagasság (ólom -távolság) |

0,50 mm |

|

Pins száma |

208 |

|

Ólomhossz (L) |

0,45 mm ~ 0,75 mm |

|

Ólomszélesség (b) |

0,17 mm ~ 0,27 mm |

|

Általános ólom -tartomány (D/E) |

30 mm ~ 30,5 mm |

|

Ülő sík (A1) |

0,05 mm ~ 0,15 mm |

|

Csomagkód |

BFQFP-208 / PQFP-208 |

LFEC3E-3QN208C gyártó

Az LFEC3E-3QN208C-t gyártja Rácsos félvezető társaság, az alacsony teljesítményű, kis formájú, programozható logikai eszközök vezető szolgáltatója.Az 1983-ban alapított és székhelye Hillsboróban, Oregon, USA, a Lattice a kommunikáció, a számítástechnika, az ipari, az autóipari és a fogyasztói alkalmazásokhoz szabott költséghatékony FPGA és CPLD megoldások szállítására összpontosít.A társaság elismerte az alacsony teljesítményű architektúrákra, a rugalmas I/O szabványokra és olyan megoldásokra, amelyek meghosszabbítják a termékek életciklusait a beágyazott és ipari piacokon.A tervezés, a támogatás és az eloszlás globális jelenlétével a rácsos félvezető továbbra is megbízható, hatékony és átprogramozható platformokat biztosít, amelyek megfelelnek mind a jelenlegi, mind a régi rendszer igényeinek.

Következtetés

Az LFEC3E-3QN208C a logikai sűrűség, a beágyazott memória, a sokoldalú I/O és a rendszeren belüli programozhatóság gyakorlati kombinációját kínálja, így jól illeszkedik a beágyazott vezérléshez, a kommunikációhoz, a prototípushoz és a műszerezéshez.A több szabvány és a rugalmas feszültség bankok támogatása biztosítja a kompatibilitást mind a modern, mind a régi rendszerekkel.Noha alacsony energiafogyasztást, költséghatékonyságot és megbízhatóságot biztosít, olyan kompromisszumokkal jár, mint a korlátozott teljesítmény és a potenciális elavulás.Összességében az eszköz továbbra is megbízható választás azok számára, akik kiegyensúlyozott FPGA -t keresnek az ipari és beágyazott alkalmazások széles skálájára.

Adatlap PDF

LFEC3E-3QN208C adatlapok:

Rólunk

ALLELCO LIMITED

Olvass tovább

Gyors lekérdezés

Kérjük, küldjön egy kérdést, azonnal válaszolunk.

Gyakran Ismételt Kérdések [FAQ]

1. Milyen eszközökre van szükségem az LFEC3E-3QN208C FPGA programozásához?

A rácsos Isplever Classic vagy Diamond szoftver segítségével programozhatja, JTAG kábellel vagy SYSConfig beállítással kombinálva.Ezek az eszközök támogatják a tervezési szintézist, a szimulációt, a bitstream generálását és a rendszeren belüli programozást.

2. Az LFEC3E-3QN208C támogatja-e az alacsony fogyasztású alkalmazásokat?

Igen, az 1,2 V-os mag és a rugalmas I/O feszültségek miatt az alacsony teljesítményű rendszerekhez megfelelő.Különösen hatékony az akkumulátorral működtetett vagy energiaérzékeny tervekben, összehasonlítva sok nagy teljesítményű FPGA-val.

3. Használhatom az LFEC3E-3QN208C-t DDR2 vagy DDR3 memóriához?

Nem, ez az FPGA hivatalosan támogatja a DDR SDRAM-ot a DDR-400-ig.A DDR2/DDR3 kompatibilitása esetén az újabb FPGA családok ajánlottak, mivel azok fejlettebb memóriavezérlőket tartalmaznak.

4. Mekkora az LFEC3E-3QN208C maximális üzemi hőmérséklete?

Általában kereskedelmi (0 ° C- +70 ° C) és ipari (-40 ° C- +85 ° C) hőmérsékleti tartományban kapható.Mindig ellenőrizze a pontos alkatrész -rendelési kódot az adatlaphoz, hogy biztosítsa a megfelelő osztályt.

5. Hogyan hasonlít az LFEC3E-3QN208C a csúcsminőségű FPGA-kkal a teljesítmény szempontjából?

Megbízható teljesítményt nyújt a középtávú alkalmazásokhoz, de nincs olyan fejlett funkció, mint a SERDES, a DSP szeletek vagy a nagyon magas logikai sűrűség.Ha szükséged van ezekre, akkor a felső kategóriájú rács vagy a versenytársak FPGA-k, például a Xilinx vagy az Intel eszközök jobban megfelelnek.

OP400HS Precision Quad OP erősítő: Jellemzők, Pinout, alkalmazások és alternatívák

2025/10/2 -en

Adv7123JST240 Video DAC: adatlap, funkciók, alkalmazások és alternatívák

2025/09/28 -en

Népszerű hozzászólások

-

Komplex utasítás beállított számítógépek: Hogyan változtatták meg a számítástechnikát?

8000/04/18 -en 147760

-

USB-C pinout és funkciók

2000/04/18 -en 111969

-

A Xilinx Unified Simulation Primitívumok használata: Átfogó útmutató az FPGA tervezéséhez és szimulációjához

1600/04/18 -en 111351

-

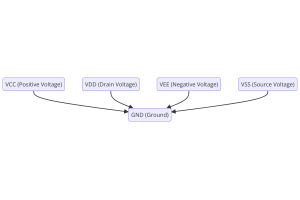

Tápfeszültségek az elektronikában: VCC, VDD, VEE, VSS és GND jelentése

0400/04/18 -en 83733

-

RJ45 Csatlakozó útmutató: Pinout, vezetékek, kábeltípusok és felhasználások

1970/01/1 -en 79520

-

A végső útmutató a vezetékes színkódokhoz a modern elektromos rendszerekben

Az, ahogyan az elektromos rendszereink a színeket használják, nem csak a megjelenéshez.Minden huzalszín most egy adott funkciót jelöl, megkönnyítve az elektromos alkatrészek azonosítását és kezelés...1970/01/1 -en 66930

-

Tisztító szelep útmutató: funkció, tünetek, tesztelés és a motor optimális teljesítményének cseréje

A tisztítószelep az autó rendszerének kulcsfontosságú része, amely segít a levegő tisztaságának megőrzésében az üzemanyag -gőzök kezelésével, mielőtt elmenekülhetnek a légkörbe.Ez nem csak a szenny...1970/01/1 -en 63080

-

Minőség (q) tényező: egyenletek és alkalmazások

A minőségi tényező, vagy a „Q” fontos, amikor ellenőrzi, hogy az induktorok és a rezonátorok hogyan működnek az elektronikus rendszerekben, amelyek rádiófrekvenciákat (RF) használnak.A 'Q' megméri,...1970/01/1 -en 63024

-

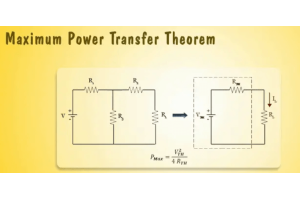

A csúcsteljesítmény elérése a maximális energiaátviteli tételgel

A maximális teljesítményátviteli tétel elmagyarázza, hogy a forrásból, például az akkumulátorból vagy a generátorból származó energia hogyan áramlik a csatlakoztatott terhelésbe.Megmutatja azt a po...1970/01/1 -en 54090

-

A23 akkumulátor specifikációi és kompatibilitása

Az A23 akkumulátor egy kicsi, hengeres alakú akkumulátor, nagy feszültséggel.A 23A, 23AE vagy MN21 néven is 12 voltos és sokkal magasabb, mint az AA vagy AAA akkumulátorok.Különleges kiala...1970/01/1 -en 52163