EP2S60F672C4 FPGA: Jellemzők, alkalmazások, programozási és adatlap útmutató

Ebben az útmutatóban egyértelmű áttekintést kap az EP2S60F672C4 -ről, amely egy erőteljes FPGA az Intel Stratix II családjának.Megtudhatja annak főbb tulajdonságait, építészetét, blokkszerkezetét és műszaki műszaki adataival, hogy megértse, hogyan illeszkedik a fejlett digitális tervekhez.Ezenkívül végigvezeti a programozási lépéseit, alkalmazásait, előnyeit és hátrányait, így pontosan láthatja, hogy hol és hogyan használható ez az eszköz.Katalógus

Mi az EP2S60F672C4?

A EP2S60F672C4 egy nagy sűrűségű FPGA az Intel-től (korábban Altera), amely a Stratix II családhoz tartozik.A 90 nm-es, 1,2 V-os réz-SRAM folyamatra épített jelentős logikai kapacitást biztosít egy 672-es FBGA csomagon belül, így ideális az összetett digitális rendszerekhez.Az EP2S sorozat részeként a „60” eszköz a Stratix II sorozat közepén és felső tartományában helyezkedik el, és a logikai sűrűség, a beágyazott memória és az I/O erőforrások erős egyensúlyát kínálja.Robusztus építészetéről és megbízhatóságáról ismert, ez az FPGA továbbra is megbízható választás sok fejlett formatervezésben.

EP2S60F672C4 -et keres?Vegye fel velünk a kapcsolatot, hogy ellenőrizze az aktuális készleteket, az átfutási időt és az árakat.

EP2S60F672C4 CAD modellek

EP2S60F672C4 szimbólum

EP2S60F672C4 lábnyom

EP2S60F672C4 3D modell

EP2S60F672C4 Jellemzők

• Fejlett 90 nm, 1,2 V CMOS folyamat

Az EP2S60F672C4-et egy 90 nm-es All-Layer réz CMOS folyamaton készítik, amely 1,2 V-os magfeszültséggel fut.Ez a technológia lehetővé teszi a nagy sebességet, a csökkentett energiafogyasztást és a nagyobb logikai sűrűségeket a régebbi FPGA generációkhoz képest.

• Adaptív logikai modul (ALM) architektúra

Az eszköz alamizsnát használ logikai építőelemeként a hagyományos logikai elemek helyett.Ez az architektúra javítja az erőforrás -felhasználást, lehetővé téve a bonyolultabb logikai funkciók hatékony megvalósítását ugyanazon a szilícium területén.

• Nagy logikai sűrűség

Körülbelül 60 440 logikai elemmel (24 176 alamizsna) az FPGA támogatja a nagy és kifinomult digitális mintákat.Ez a nagy kapacitás alkalmassá teszi az olyan alkalmazásokra, mint a jelfeldolgozás, a kommunikáció és a beágyazott vezérlőrendszerek.

• Trimatrix ™ on-chip memória

Az EP2S60F672C4 három típusú RAM-blokkot (M512, M4K és M-RAM) integrál, hogy összesen körülbelül 2,4 mbit beágyazott memóriát biztosítson.Ez a keverék lehetővé teszi a kis FIFO-k, a közepes pufferek és a nagy kettős portos emlékek hatékony megvalósítását.

• Dedikált DSP blokkok

Az eszköz 36 dedikált DSP -blokkot tartalmaz, amelyeket számtani műveletekhez terveztek, például szorzás, felhalmozódás és FIR szűrés.Ezek a blokkok növelik a számítás-igényes feladatok teljesítményét, miközben megtakarítják az általános logikai erőforrásokat.

• Nagysebességű I/O és jel integritása

Támogatja a különféle egy végű és differenciális I/O szabványokat, valamint a dinamikus fázis-igazítási (DPA) áramkört.Ezek a szolgáltatások lehetővé teszik a stabil, nagysebességű adatátvitelt akár 1 Gbps-ig, biztosítva a megbízható kommunikációt a külső komponensekkel.

• Gazdag külső memória interfész támogatás

Az FPGA kompatibilis a DDR, DDR2, QDR II, RLDRAM II és egyéb memóriaszabványokkal.A beépített interfész támogatás egyszerűsíti a tábla tervezését és magas adatátviteli sebességet ér el a memóriaigényes alkalmazásokhoz.

• Rugalmas órakezelés

Legfeljebb 12 on-chip PLL lehetővé teszi az óra szorzását, az osztást, a fázisváltást és a hibamentes váltást.Finomíthatja az óratomineket és csökkentheti a zaklatást, támogatva a belső órafrekvenciákat akár 500–550 MHz-ig.

• Bitstream titkosítás és újrakonfiguráció

Az EP2S60F672C4 támogatja az AES-alapú bitstream titkosítást a szellemi tulajdon biztosítása érdekében.Ezenkívül távoli újrakonfigurációs képességet is kínál, lehetővé téve a helyszíni frissítéseket az eszköz cseréje nélkül.

Stratix II blokkdiagram

A Stratix II blokkdiagramja, amint az az EP2S60F672C4 esetében látható, szemlélteti a logika, a memória és a DSP erőforrások belső elrendezését, amelyek az FPGA magját képezik.A logikai tömb blokkok (laboratóriumok) egy szokásos rácsban vannak elrendezve, beágyazott RAM és DSP oszlopok körülvéve, amelyek gyors aritmetikai és chip tárolási képességeket biztosítanak.A perifériás I/O elemek és az órahálózatok keretezik ezt a struktúrát, lehetővé téve az adatátvitel és az időzítés vezérlését az FPGA és a külső eszközök között.Ez a diagram azért fontos, mert segít megérteni a különféle funkcionális blokkok fizikailag szerveződését, lehetővé téve számukra az elhelyezés, az útválasztás és az általános rendszer teljesítményének optimalizálását.

Stratix II I/O Banks diagram

Ez a Stratix II I/O Banks diagram szemlélteti, hogy az EP2S60F672C4 bemeneti/kimeneti csapjai hogyan vannak csoportosítva, és milyen elektromos szabványokat támogatnak az egyes csoportok.Minden I/O bankot úgy terveztek, hogy kezelje a meghatározott feszültségszinteket, jelzési típusokat és olyan funkciókat, mint például az LVTTL, az SSTL, az LVD -k vagy az óra bemeneti szabványok.Az elrendezés megmutatja, hogy a különféle bankok (például 1, 2, 5, 6 vs. 3, 4, 7, 8 stb.) Hogyan optimalizálódnak az általános célú I/O vagy a nagysebességű differenciáljelzéshez, ideértve az LVDS/LVPECL óramenetek támogatását a széleken.Ennek a struktúrának a megértése fontos a csapok hozzárendelésekor, mivel a megfelelő bankválasztás biztosítja az elektromos kompatibilitást, egyszerűsíti a táblák útválasztását, és maximalizálja az FPGA teljesítményét a nagysebességű tervekben.

EP2S60F672C4 specifikációk

|

Beír |

Paraméter |

|

Gyártó |

Altera/intel |

|

Sorozat |

Stratix® II |

|

Csomagolás |

Tálca |

|

Alkatrész állapota |

Elavult |

|

Labs/CLB -k száma |

3022 |

|

A logikai elemek/cellák száma |

60,440 |

|

Összes RAM BITS |

2,544,192 |

|

I/O száma |

492 |

|

Feszültség - ellátás |

1,15 V ~ 1,25 V |

|

Szerkesztési típus |

Felszíni |

|

Üzemi hőmérséklet |

0 ° C ~ 85 ° C (TJ) |

|

Csomag / tok |

672-BBGA |

|

Beszállító eszköz csomag |

672-FBGA (27 × 27) |

|

Alaptermék száma |

EP2S60 |

EP2S60F672C4 alkalmazások

1. digitális jelfeldolgozás (DSP) és szűrés

Az EP2S60F672C4 jól alkalmas nagy teljesítményű DSP funkciók, például FIR és IIR szűrők, FFT feldolgozás és összetett aritmetikai műveletek megvalósítására.Dedikált DSP -blokkjai hatékonyan kezelik a szorzás és a felhalmozódásokat, felszabadítva az általános logikai erőforrásokat más feladatokhoz.Az On-Chip Trimatrix ™ memória lehetővé teszi a sima adatpufferelést és a csővezetéket, ami kiválóan alkalmas valós idejű feldolgozáshoz, magas minta sebességgel.Ez az eszközt ideálissá teszi a fejlett audio, video- és radarjel -alkalmazásokhoz.

2. nagysebességű kommunikáció és hálózatépítés

Az FPGA nagysebességű I/O interfészei és a dinamikus fázis-igazítás (DPA) áramköri támogatása megbízható, gigabites szintű adatátvitel.Kommunikációs protokollokat és fizikai réteg funkciókat képes végrehajtani olyan rendszerekhez, mint az útválasztók, kapcsolók és a hátlapok összekapcsolása.Nagy logikai kapacitása és rugalmas PLL-jeivel képes kezelni a komplex időzítést és a protokoll konverziót a többszörös sebességű interfészek között.Ezek a képességek miatt a telekommunikációs infrastruktúra és a nagy sávszélességű hálózati berendezések erőteljesen megfelelnek.

3. memóriavezérlők és adatfeldolgozó rendszerek

Az EP2S60F672C4 különféle külső memória interfészeket támogat, beleértve a DDR, DDR2, RLDRAM II és QDR II-t, ideális ezáltal a nagy sávszélességű memóriavezérlők megtervezéséhez.Nagy sebességgel képes kezelni az adatpufferelést, a címgenerációt és a választottbírósági eljárást, minimális késéssel.A gyors órahálózatok és a beágyazott RAM -blokkok kombinációja lehetővé teszi a nagy adatfolyamok hatékony kezelését.Ez teszi az FPGA -t a képfeldolgozáshoz, a video streaming és a tudományos számítási platformokhoz, amelyek a nehéz adatátviteli sebességre támaszkodnak.

4. Egyéni logika és beágyazott gyorsulás

Több mint 60 000 logikai elemmel és gazdag órakezeléssel az FPGA testreszabott hardvergyorsítókat tárolhat meghatározott algoritmusokhoz.A tervezők gyakran használják azt a CPU-kból számítási intenzív feladatok, például titkosítás, protokoll elemzés vagy valós idejű vezérlési hurkok letöltésére.Több funkcionális blokkot is integrálhat, így alkalmassá teszi a komplex SOC-szerű mintákhoz.Ez a rugalmasság értékessé teszi az olyan alkalmazásokban, mint az ipari automatizálás, a biztonsági rendszerek és a repülőgép -vezérlő egységek.

5. Prototípus -készítési és oktatási fejlesztési platformok

Az EP2S60 készüléket általában a prototípus készítéséhez, a teszteléshez és az akadémiai kutatáshoz használt FPGA fejlesztési készleteken találják meg.A logikai kapacitás, az I/O szám és a DSP képességek egyensúlya lehetővé teszi a mérnököknek és a hallgatóknak a teljes rendszerek végrehajtását és ellenőrzését egyetlen chipen.Támogatja a digitális tervek gyors iterációját, lehetővé téve a hardver ellenőrzését, mielőtt elkötelezi magát az ASIC fejlesztése mellett.Számos egyetem és K + F laboratórium használja azt a fejlett digitális tervezési és jelfeldolgozási koncepciók tanításához.

EP2S60F672C4 Hasonló alkatrészek

|

Meghatározás |

EP2S60F672C4 |

EP2S60F672C3N |

EP2S60F672C5 |

EP2S60F672C5N |

EP2S60F672I4

|

EP2S60F672I3N |

|

Család / sorozat |

II. Stratix |

II. Stratix |

II. Stratix |

II. Stratix |

II. Stratix |

II. Stratix |

|

Logikai elemek (LE) |

60,440 |

60,440 |

60,440 |

60,440 |

60,440 |

60,440 |

|

Alamizsna |

24,176 |

24,176 |

24,176 |

24,176 |

24,176 |

24,176 |

|

Csomag |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

|

Sebesség -fokozat |

C4 (STD) |

C3 (gyorsabb) |

C5 (gyorsabb) |

C5 (gyorsabb) |

I4 (std) |

I3 (gyorsabb) |

|

Hőmérsékleti fokozat |

Kereskedelmi (0 ~ 70 ° C) |

Kereskedelmi |

Kereskedelmi |

Kereskedelmi |

Ipari (−40 ~ 100 ° C) |

Ipari (−40 ~ 100 ° C) |

|

I/O csapok |

492 |

492 |

492 |

492 |

492 |

492 |

|

Chip memória |

2.4 MBit |

2.4 MBit |

2.4 MBit |

2.4 MBit |

2.4 MBit |

2.4 MBit |

|

Magfeszültség |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

1.2 V |

|

Kulcsfontosságú különbség |

Alapvető kereskedelmi sebesség |

C3 sebességű tartály, ólommentes „N” |

Nagyobb sebességű tartály |

Nagyobb sebességű tartály, „N” változat |

Ipari hőmérséklet, azonos sűrűség |

Ipari, gyorsabb, gyorsabb, ólommentes |

EP2S60F672C4 programozási lépések

Mielőtt használhatja az EP2S60F672C4 FPGA -t a kialakításban, megfelelően kell konfigurálnia azt az összeállított bitream segítségével.Ez a folyamat magában foglalja a programozási fájl elkészítését, a hardver felületének beállítását és annak biztosítását, hogy a konfiguráció megfelelően betöltse a bekapcsolást.

1. lépés: Készítse el és állítsa össze a formatervezést

Először az Intel Quartus II szoftver segítségével fejleszti ki a logikai kialakítást.A formatervezés kitöltése után összeállítja azt a programozási fájlt (.sof vagy .pof) létrehozásához, kifejezetten az EP2S60F672C4 eszközhöz.Az összeállítási folyamat ellenőrzi az időzítést, a PIN -hozzárendeléseket és az erőforrás -felhasználást annak biztosítása érdekében, hogy a tervezés illeszkedjen az FPGA architektúrájához.Összeállítása után a bitstream készen áll az eszköz konfigurációjára.

2. lépés: Állítsa be a programozási hardvert

Ezután elkészíti a PC és az FPGA tábla közötti fizikai programozási felületet.Ez általában magában foglalja az USB-blaster vagy kompatibilis JTAG-kábel csatlakoztatását az eszköz JTAG portjához.Ellenőrizze, hogy a Quartus II felismeri -e a programozót, és hogy a céleszközt megfelelően észlelik -e.Ez a lépés biztosítja a stabil kommunikációt a konfigurációs folyamat megkezdése előtt.

3. lépés: Töltse be a programozási fájlt az eszközbe

A Quartus II Programozó eszköz használatával hozzáadja a CSOGULT .SOF vagy a .POF fájlt, és kiválasztja az EP2S60F672C4 -et az észlelt eszközlistából.Ezután elindítja a programozási szekvenciát, amelynek során a bitstream átkerül és betölti az FPGA SRAM konfigurációs cellájába.A sikeres konfiguráció megerősítéséhez figyelemmel kell kísérnie az előrehaladási sávot és az állapotüzeneteket.Miután befejeződött, az FPGA azonnal megkezdi a programozott logika végrehajtását.

4. lépés: Ellenőrizze a konfigurációt és a műveletet

A programozás után ellenőrzi, hogy az eszköz a tervezett módon működik -e.A Quartus II ellenőrzési lehetőséget kínál a CRC és az állapotjelek konfigurációjának ellenőrzésére, biztosítva, hogy a terv megfelelően betölthető legyen.Kipróbálhatja az I/O funkciókat is, vagy futtathat egy funkcionális szimulációt a rendszer viselkedésének megerősítésére.Ez az utolsó lépés biztosítja, hogy a tervezés teljesen működőképes és stabil legyen a hardveren.

EP2S60F672C4 előnyök és hátrányok

Előnyök

• Magas logikai sűrűség az összetett mintákhoz

• Jó teljesítmény-költség arány

• Könnyű migráció ugyanabban a családon belül

• Stabil és érett fejlesztési eszközök

• Bizonyított megbízhatóság az ipari felhasználásban

Hátrányok

• Elavult és nehezebb forrás

• Magasabb energiafogyasztás, mint az újabb FPGA -k

• Nincsenek modern, nagysebességű adó-vevők

• Nehezebb időzítés bezárása a nagy felhasználáskor

• Korlátozott méretezhetőség a jövőbeli protokollokhoz

EP2S60F672C4 csomagolási méretek

|

Beír |

Paraméter |

|

Csomagtípus |

672-FBGA (Fineline BGA) |

|

Testméret (l × w) |

27,00 mm × 27,00 mm |

|

Teljes csomagmagasság (A) |

Max 3,50 mm |

|

Kiemelkedő magasság (A1) |

Min 0,30 mm |

|

Szubsztrát vastagsága (A2) |

Max 3,00 mm |

|

Golyó átmérője (b) |

0,50 mm - 0,70 mm |

|

Golyó hangmagasság (e) |

1,00 mm |

|

A golyók száma |

672 |

|

Szerelési stílus |

Felszíni |

|

Csomagleírás |

FBGA, 27 × 27 mm rács |

EP2S60F672C4 gyártó

Az EP2S60F672C4 FPGA -t gyártja Altera Corporation, a programozható logikai eszközök vezető úttörője.2015 -ben az Altera -t megszerezte Intell, és a termék most az Intel Programmable Solutions Group (PSG) alá tartozik, amely továbbra is támogatja és ellátja az ALTERA létrehozott FPGA családjait.Az Intel fenntartja a Stratix II vonalat a Legacy termékportfólió részeként, biztosítva a dokumentációt, az eszköz támogatását és az ipari és kommunikációs alkalmazások hosszú távú elérhetőségét.

Következtetés

Az EP2S60F672C4 a nagy logikai sűrűség, a rugalmas memória architektúrát és a robusztus I/O funkciókat egyesíti a komplex digitális rendszerek támogatása érdekében.ALM-alapú kialakítása, a Trimatrix ™ memória, a DSP blokkok és az órakezelési szolgáltatások lehetővé teszik az igényes alkalmazások hatékony megvalósítását.Noha bizonyított megbízhatóságot és érett fejlesztési támogatást kínál, korlátozásokkal kell szembenéznie, például az elavulás és a modern adó -vevők hiánya az újabb FPGA generációkhoz képest.Összességében a kiegyensúlyozott teljesítmény és sokoldalúság szilárd választássá teszi a jelfeldolgozás, a kommunikáció, az adatkezelés és a prototípus -alkalmazások számára.

Adatlap PDF

EP2S60F672C4 adatlapok:

Rólunk

ALLELCO LIMITED

Olvass tovább

Gyors lekérdezés

Kérjük, küldjön egy kérdést, azonnal válaszolunk.

Gyakran Ismételt Kérdések [FAQ]

1. Működhet -e az EP2S60F672C4 a modern DDR memória interfészekkel?

Igen, támogatja a DDR, DDR2, QDR II és RLDRAM II interfészeket, amelyek számos közös külső memória -standardot fednek le.Ez lehetővé teszi a nagy sávszélességű adatfeldolgozó alkalmazásokhoz.

2. Az EP2S60F672C4 speciális kezelést vagy tárolást igényel?

Igen, mint más BGA-csomagolású alkatrészek, a nedvességvezérelt csomagolásban is tárolni kell és ESD-védelemmel kell kezelni.A megfelelő tárolási gyakorlatok követése elősegíti a forraszthatóság és az eszköz megbízhatóságának fenntartását az összeszerelés során.

3. Hogyan csökkentheti az energiafogyasztást az EP2S60F672C4 tervekben?

Ha lehetséges, optimalizálhatja a logikai felhasználást, a kapu fel nem használt óráit, az alacsonyabb I/O feszültségeket, és kihasználhatja az energiatudományi szintézis lehetőségeit a Quartus II-ben, hogy minimalizálja az általános energiafelvételeket.

4. Milyen programozási eszközökre van szükség az EP2S60F672C4 -hez?

Szüksége lesz az Intel Quartus II szoftverre a tervezéshez, az összeállításhoz és a programozáshoz, valamint az eszköz konfigurálásához USB-blaster vagy kompatibilis JTAG kábel.

5. Az EP2S60F672C4 támogatást vagy a távoli újrakonfigurációt támogatja-e?

Igen, támogatja az AES-alapú bittream titkosítást és a távoli újrakonfigurációt, lehetővé téve a rendszer biztonságos frissítését anélkül, hogy az FPGA fizikailag cserélné.

Mindent az LFXP6C-3FN256C Lattice Semiconductorról

2025/10/6 -en

XC2C256-7TQ144C CPLD: Pinout, szolgáltatások, programozási és adatlap útmutató

2025/10/3 -en

Népszerű hozzászólások

-

Komplex utasítás beállított számítógépek: Hogyan változtatták meg a számítástechnikát?

8000/04/19 -en 147782

-

USB-C pinout és funkciók

2000/04/19 -en 112062

-

A Xilinx Unified Simulation Primitívumok használata: Átfogó útmutató az FPGA tervezéséhez és szimulációjához

1600/04/19 -en 111352

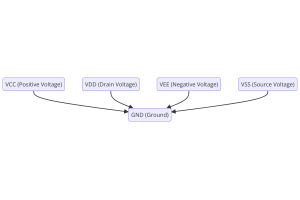

-

Tápfeszültségek az elektronikában: VCC, VDD, VEE, VSS és GND jelentése

0400/04/19 -en 83819

-

RJ45 Csatlakozó útmutató: Pinout, vezetékek, kábeltípusok és felhasználások

1970/01/1 -en 79639

-

A végső útmutató a vezetékes színkódokhoz a modern elektromos rendszerekben

Az, ahogyan az elektromos rendszereink a színeket használják, nem csak a megjelenéshez.Minden huzalszín most egy adott funkciót jelöl, megkönnyítve az elektromos alkatrészek azonosítását és kezelés...1970/01/1 -en 66999

-

Tisztító szelep útmutató: funkció, tünetek, tesztelés és a motor optimális teljesítményének cseréje

A tisztítószelep az autó rendszerének kulcsfontosságú része, amely segít a levegő tisztaságának megőrzésében az üzemanyag -gőzök kezelésével, mielőtt elmenekülhetnek a légkörbe.Ez nem csak a szenny...1970/01/1 -en 63124

-

Minőség (q) tényező: egyenletek és alkalmazások

A minőségi tényező, vagy a „Q” fontos, amikor ellenőrzi, hogy az induktorok és a rezonátorok hogyan működnek az elektronikus rendszerekben, amelyek rádiófrekvenciákat (RF) használnak.A 'Q' megméri,...1970/01/1 -en 63062

-

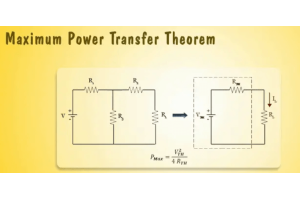

A csúcsteljesítmény elérése a maximális energiaátviteli tételgel

A maximális teljesítményátviteli tétel elmagyarázza, hogy a forrásból, például az akkumulátorból vagy a generátorból származó energia hogyan áramlik a csatlakoztatott terhelésbe.Megmutatja azt a po...1970/01/1 -en 54097

-

A23 akkumulátor specifikációi és kompatibilitása

Az A23 akkumulátor egy kicsi, hengeres alakú akkumulátor, nagy feszültséggel.A 23A, 23AE vagy MN21 néven is 12 voltos és sokkal magasabb, mint az AA vagy AAA akkumulátorok.Különleges kiala...1970/01/1 -en 52215