EP1C4F400C8 FPGA: Jellemzők, specifikációk, programozás és alternatívák

Ha a programozható logikával dolgozik, az EP1C4F400C8 gyakorlati egyenleget biztosít a teljesítmény és a költségek.Ebben a cikkben megtudhatja, mi ez az FPGA, annak legfontosabb jellemzői, mint a logikai kapacitás, a memória és az I/O opciók, és hogy a szerkezete hogyan támogatja a megbízható kialakítást.Látni fogja annak előírásait, alkalmazásait a rendszerekben, a programozási folyamatban és annak összehasonlításának módja a hasonló részekhez.Katalógus

Mi az EP1C4F400C8?

A EP1C4F400C8 tagja az Intel (korábban Altera) Cyclone FPGA családjának, amelyet költséghatékony és megbízható programozható logikai megoldásként terveztek.A 0,13 µm SRAM folyamatra épített eszköz mérsékelt logikai sűrűségű és rugalmas I/O opciókat kínál egy kompakt FBGA-400 csomagon belül.A cikloncsaládot, amely olyan eszközöket is magában foglal, mint az EP1C3, EP1C6, EP1C12 és EP1C20, a méretezhető tervek teljesítményének és megfizethetőségének kiegyensúlyozására hozták létre, lehetővé téve a sűrűségszintek és a csomagok közötti egyszerű migrációt.A stabilitásról és a széles körű örökbefogadásról ismert, továbbra is megbízható választás a Legacy Designs -ban.

EP1C4F400C8 -at keres?Vegye fel velünk a kapcsolatot, hogy ellenőrizze az aktuális készleteket, az átfutási időt és az árakat.

EP1C4F400C8 CAD modellek

EP1C4F400C8 szimbólum

EP1C4F400C8 lábnyom

EP1C4F400C8 3D modell

EP1C4F400C8 Jellemzők

• Logikai kapacitás

Az EP1C4F400C8 mintegy 4000 logikai elemet kínál, 400 logikai tömb blokkokba (LABS) szervezve.Ez alkalmassá teszi a középtávú tervekhez, amelyek mérsékelt logikai sűrűségűek, miközben megőrzik a költséghatékonyságot.

• Beágyazott memória

Körülbelül 76,5 kbit beágyazott memóriát integrál.Ez a belső RAM támogatja az adatpufferelést, a tárolást és a kis memóriafunkciókat, csökkentve a külső memóriakomponensek szükségességét számos tervben.

• Magas I/O szám

Az eszköz 301 felhasználó-konfigurálható I/O csapot biztosít a 400 golyó FBGA csomagjában.Ez a magas PIN -kód lehetővé teszi a gazdag kapcsolatot a több perifériás interfészhez szükséges komplex rendszerek számára.

• Széles körű I/O szabványok támogatása

Támogatja a több I/O szabványt, beleértve az LVTTL, LVCMOS, SSTL-2, SSTL-3 és differenciális LVD-ket.Ez a rugalmasság lehetővé teszi az FPGA számára, hogy közvetlenül kapcsolódjon a különféle modern logikai családokhoz és memóriakészülékekhez.

• Nagy sebességű differenciáljelzés

Az LVDS támogatásával akár 640 Mbps támogatást nyújt, az FPGA kezeli a gyors adatátviteli követelményeket.Ez praktikussá teszi az olyan alkalmazások számára, mint a nagysebességű kommunikációs kapcsolatok és a gyors digitális interfészek.

• Órakezelés PLL -ekkel

A chip két fázisú hurkot (PLL) és nyolc globális órahálózatot integrál.Ezek a tulajdonságok lehetővé teszik a pontos óra előállítását, a szorzást és a jitter-vezérlést az időzítés-kritikus alkalmazásokhoz.

• Alacsony feszültségű alaptevékenység

Névleges 1,5 V -os magfeszültséggel működve az eszköz a teljesítményt az alacsonyabb energiafogyasztással egyensúlyozza.Ezt a feszültségszintet optimalizáltuk a gyártásához használt 0,13 um CMOS technológiára.

• Rugalmas I/O feszültségek

Az FPGA 1,5 V, 1,8 V, 2,5 V és 3,3 V I/O feszültséget támogat a különböző bankokban.Ez a sokoldalúság lehetővé teszi, hogy összekapcsolódjon mind a régi, mind a modern rendszer komponensekkel.

• SRAM-alapú konfiguráció

A többi ciklon FPGA-khoz hasonlóan SRAM-alapú, és minden bekapcsoláskor újrakonfigurálást igényel.Ez rugalmasságot biztosít a frissítésekhez, de szükség van egy külső konfigurációs eszközre vagy vezérlőre is.

• Bitstream tömörítési támogatás

Az EP1C4F400C8 támogatja a tömörített bitstream betöltését a konfiguráció során.Ez csökkenti a külső memóriaigényeket és felgyorsítja a konfigurációs időket.

• PCI -megfelelés

Ez magában foglalja a PCI szabványok beépített támogatását (33/66 MHz, 32/64 bites).Ez a szolgáltatás lehetővé teszi, hogy az eszköz közvetlenül integrálódjon olyan rendszerekbe, amelyek a PCI interfészek további áthidaló logikája nélkül.

Ciklon laboratóriumi felépítés

Az ábra a logikai tömb blokk (LAB) szerkezetét mutatja, amelyet az FPGA -k ciklonban használnak, mint például az EP1C4F400C8.Minden laboratórium csatlakozik az összeköttetések hálózatához: sor összekapcsolások, oszlopok összekapcsolása és a helyi összekapcsolások, amelyek a logikai elemek és más blokkok közötti jeleket irányítják.A közvetlen kapcsolat összekapcsolása gyors, alacsony késleltetésű útvonalakat biztosít a szomszédos laboratóriumokhoz, javítva az időzítési teljesítményt a jelútokon.Ez az architektúra azért fontos, mert egyensúlyba hozza az útválasztási rugalmasságot a hatékonysággal, lehetővé téve az FPGA számára, hogy kezelje a komplex mintákat, miközben a sebességet és a területet optimalizálva tartja.

Ciklon I/O bankok diagramja

A diagram szemlélteti az FPGA -k ciklon I/O bank szerkezetét, mint például az EP1C4F400C8.A készüléket négy I/O bankra osztják, amelyek mindegyike saját ellátási buszával rendelkezik, lehetővé téve a különböző feszültségszabványok keverését egyetlen FPGA -n belül.Minden bank az I/O szabványok széles skáláját támogatja, beleértve az LVTTL, LVCMOS, LVD-k, RSD-k és SSTL, míg az 1. és 3. bank szintén támogatja a 3.3 V-os PCI-t a Legacy Systems-szel való kompatibilitás szempontjából.Ez a rugalmas I/O architektúra fontos, mivel lehetővé teszi a zökkenőmentes integrációt a különféle külső eszközökkel és interfészekkel, így az FPGA alkalmazkodhat a különféle alkalmazásokhoz.

EP1C4F400C8 specifikációk

|

Beír |

Paraméter |

|

Gyártó |

Altera/intel |

|

Sorozat |

Cyclone® |

|

Csomagolás |

Tálca |

|

Alkatrész állapota |

Elavult |

|

Labs/CLB -k száma |

400 |

|

A logikai elemek/cellák száma |

4000 |

|

Összes RAM BITS |

78,336 |

|

I/O száma |

301 |

|

Feszültség - ellátás |

1,425V ~ 1,575 V |

|

Szerkesztési típus |

Felszíni |

|

Üzemi hőmérséklet |

0 ° C ~ 85 ° C (TJ) |

|

Csomag / tok |

400-BGA |

|

Beszállító eszköz csomag |

400-FBGA (21 × 21) |

|

Alaptermék száma |

EP1C4 |

EP1C4F400C8 alkalmazások

1. Digitális jelfeldolgozás (DSP)

Az EP1C4F400C8 programozható olyan feladatok elvégzésére, mint a szűrés, az FFT és a Signal Modulation.A logikai elemek és a beágyazott memória kombinációja lehetővé teszi a nagysebességű feldolgozáshoz.Ez lehetővé teszi, hogy a hagyományos DSP chipeket rugalmas FPGA -megoldással cserélje ki, amelyet különféle algoritmusok esetén átprogramozhatunk.

2. beágyazott és vezérlő rendszerek

Ipari és beágyazott rendszerekben ezt az FPGA -t gyakran használják az egyedi vezérlők, szekvenciák és állami gépek megvalósításához.Újrakonfigurálható logikája lehetővé teszi a hardver viselkedésének pontosan a rendszer igényeihez való testreszabását.A kontroll logika integrálásával az FPGA -ban csökken a külső alkatrészek száma, javítva a megbízhatóságot és a költségek csökkentését.

3. Kommunikáció és interfész áthidalása

Az eszköz támogatja a több I/O szabványt, és hídként működhet a különböző kommunikációs protokollok között.Gyakran használják a PCI, LVD -k, SDRAM és más interfészek összekapcsolására egy rendszeren belül.Ez nagyon hasznossá teszi a hálózati berendezésekben, a beágyazott vezérlőkben és a régi interfész konverziókban.

4. Adat megszerzése és feldolgozása

Magas I/O rendelkezésre állással és rugalmas memóriával az EP1C4F400C8 alkalmas az adatgyűjtő rendszerekhez.Közvetlenül kapcsolatba léphet az ADC -kkel és érzékelőkkel, időben feldolgozhatja az adatokat, és elkészítheti azt tárolásra vagy átvitelre.Az ilyen alkalmazások gyakoriak az orvosi műszerekben, a vizsgálati berendezésekben és a tudományos mérőeszközökben.

EP1C4F400C8 Hasonló alkatrészek

|

Meghatározás |

EP1C4F400C8 |

EP1C4F400C8N |

EP1C4F400C8NAA |

EP1C4F400C6N |

EP1C4F324C8N |

EP1C4T144C8N |

|

Gyártó |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

|

FPGA család |

Ciklon (EP1C4) |

Ciklon (EP1C4) |

Ciklon (EP1C4) |

Ciklon (EP1C4) |

Ciklon (EP1C4) |

Ciklon (EP1C4) |

|

Logikai elemek (LES) |

4000 |

4000 |

4000 |

4000 |

4000 |

4000 |

|

Beágyazott memória (bitek) |

~ 76,5 kbit |

~ 76,5 kbit |

~ 76,5 kbit |

~ 76,5 kbit |

~ 76,5 kbit |

~ 76,5 kbit |

|

I/O csapok |

301 |

301 |

301 |

301 |

249 |

97 |

|

Csomag / tok |

400-FBGA |

400-FBGA |

400-FBGA |

400-FBGA |

324-FBGA |

144-TQFP |

|

Sebesség -fokozat |

C8 |

C8 |

C8 |

C6 (gyorsabb) |

C8 |

C8 |

|

Magfeszültség |

1,5 V |

1,5 V |

1,5 V |

1,5 V |

1,5 V |

1,5 V |

|

Működési hőmérséklet.Hatótávolság |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C |

0 ° C ~ 85 ° C

|

EP1C4F400C8 programozási lépések

Mielőtt használhatja az EP1C4F400C8 FPGA -t, be kell töltenie a tervét az eszközbe.A programozás magában foglalja az FPGA konfigurálását egy bitstream fájllal, hogy tudja, hogyan kell viselkedni a kívánt áramkörként.

1. Válassza ki a konfigurációs sémát és állítsa be az MSEL -csapokat

Először azt a konfigurációs sémát választja, amely a legjobban illeszkedik a beállításhoz, mint például az aktív soros, passzív soros vagy a JTAG.Ezt úgy végezzük, hogy az MSEL-csapokat meghatározott logikai szintre állítják a bekapcsolás előtt.Mindegyik mód különböző csapokat és protokollokat használ, ezért meg kell erősítenie a kompatibilitást a tervezési eszközökkel és a konfigurációs memóriával.A helyes választás itt biztosítja a zökkenőmentes konfigurációs folyamatot.

2. Alkalmazza az eszközt és inicializálja az eszközt

Ezután kapcsolja be az FPGA mag- és I/O síneit a megadott feszültségtartományokban.Az indítás során tartsa alacsonyan az NConfig PIN -kódot, hogy a készüléket visszaállítsák, amíg a tápfeszültség stabil nem lesz.Ha stabil, akkor az NSTATUS PIN -kóddal felszabadítja a RESET és az eszköz jeleit.Ez garantálja, hogy az FPGA megfelelően inicializálódik a konfiguráció megkezdése előtt.

3. Adja át a konfigurációs bitstream -t

Ebben a szakaszban elküldi a konfigurációs adatfájlt (bitstream) az FPGA -ba a kiválasztott séma segítségével.Aktív soros vagy passzív soros módban a bitstream külső memóriakészülékből származik, míg a JTAG lehetővé teszi a közvetlen programozást kábel útján.Az eszköz folyamatosan olvassa el a konfigurációs adatokban, amíg nem fejeződik be.A tervezési szoftver előállítja ezt a bitstream -et, hogy megfeleljen a logikai követelményeknek.

4. Erősítse meg a sikeres konfigurációt (conf_done)

Amikor az FPGA befejezi a betöltését, azt állítja, hogy a Conf_Done PIN -kódot megmutatja, hogy a konfigurációs adatok sikeresen megkapták.Ugyanakkor az eszköz belső inicializációt hajt végre, például a tisztítás nyilvántartásait és az I/O aktiválását.Ha a conf_done nem sikerül magasra emelkedni, ez általában azt jelenti, hogy a konfigurációs adatoknak vagy a beállításnak hibája van.Figyelem, hogy ez a PIN -kód a legegyszerűbb módja annak, hogy ellenőrizze, hogy a folyamat befejeződött -e.

5.

Végül lehetősége van az FPGA frissítésére vagy átprogramozására anélkül, hogy eltávolítaná azt a tábláról.A JTAG vagy egy beágyazott vezérlő használatával közvetlenül betöltheti az új bitream -t, amely hasznos a firmware frissítéseihez.Ez a rugalmasság lehetővé teszi a rendszer módosítását, hibakeresését vagy frissítését is a telepítés után.Biztosítja, hogy az FPGA-alapú kialakítás idővel alkalmazkodjon a változó követelményekhez.

EP1C4F400C8 Előnyök és hátrányok

Előnyök

• Költséghatékony választás a középkategóriás tervekhez

• Magas I/O szám a hasonló sűrűségű eszközökhöz képest

• Rugalmas feszültség és I/O szabványos támogatás

• Érett eszközök és dokumentáció támogatja

• Alacsonyabb energiafelhasználás, mint az idősebb FPGA generációk

Hátrányok

• Elavult, korlátozott hosszú távú elérhetőséggel

• Alacsonyabb logikai és memóriakapacitás, szemben a modern FPGA -kkal

• Lassabb működési sebesség és I/O teljesítmény

• A konfigurációhoz külső memória szükséges a bekapcsoláshoz

• Hiányzik a fejlett funkciók, például a DSP blokkok és a nagysebességű adó-vevők

EP1C4F400C8 Csomagolási méretek

|

Beír |

Paraméter |

|

Csomagtípus |

FBGA (Finom-Pitch gömbrács tömb) |

|

Golyószám |

400 |

|

Golyó hangmagasság (e) |

1,0 mm (jellemző az EP1C4F400 ciklonra) |

|

Golyó átmérője (b) |

0,45 mm (névleges) |

|

Csomagméret (d × E) |

21 mm × 21 mm |

|

Csomagmagasság (A) |

2,40 mm (max) |

|

Szubsztrát vastagsága (A2) |

~ 0,40 mm |

|

Penész sapka vastagsága (A3) |

~ 1,90 mm |

|

Golyómagasság (A1) |

0,25 mm (névleges) |

|

A1 csap |

Az orientációra megjelölt |

|

Tömb elrendezése |

20 × 20 rács (hiányzik a sarokgolyók) |

|

Felszerelés |

Felszíni tartó (SMD) |

EP1C4F400C8 gyártó

Az EP1C4F400C8 -ot eredetileg gyártotta Altera Corporation, úttörő a programozható logikai eszközökben és az FPGA technológiában.2015 -ben az Altera -t megszerezte Intel Corporation, és a termékcsalád az Intel Programmable Solutions Group (PSG) részévé vált.Manapság az Intel támogatja ezeket a Legacy Altera eszközöket, miközben a fejlesztést az újabb FPGA családokra összpontosítja, biztosítva a meglévő felhasználók folytonosságát és a programozható logika innovációjának előmozdítását.

Következtetés

Az EP1C4F400C8 költséghatékony és sokoldalú FPGA-ként áll ki, amely szilárd teljesítményt nyújt a középkategóriás tervekhez.4000 logikai elemével, beágyazott memóriájával, kiterjedt I/O -támogatásával és kompatibilitással több feszültség- és interfész szabványokkal, rugalmasságot biztosít a változatos alkalmazások között.Építészete, programozási folyamata és a DSP, beágyazott rendszerek és az adatgyűjtés széles körű használhatósága gyakorlati választássá teszi örökségének ellenére.Noha hiányzik az újabb eszközökben található fejlett funkciók, és korlátozott hosszú távú elérhetőséggel rendelkeznek, továbbra is megbízható lehetőség, hogy bevált megoldásokat keressen a skálázható FPGA tervekben.

Adatlap PDF

EP1C4F400C8 adatlapok:

Rólunk

ALLELCO LIMITED

Olvass tovább

Gyors lekérdezés

Kérjük, küldjön egy kérdést, azonnal válaszolunk.

Gyakran Ismételt Kérdések [FAQ]

1. Milyen eszközökre van szükség az EP1C4F400C8 programozásához?

Szüksége van az Intel Quartus szoftverére (korábban Altera Quartus II), valamint egy támogatott programozási kábellel, például az USB-Blaster-rel.Ezek az eszközök lehetővé teszik a bitream létrehozását és az FPGA -ba történő betöltését.

2. Az EP1C4F400C8 képes -e közvetlenül kezelni a PCI alkalmazásokat?

Igen, beépített megfeleléssel rendelkezik a PCI szabványokhoz (33/66 MHz, 32/64 bites), így alkalmassá teszi a PCI-alapú rendszerintegrációra anélkül, hogy extra áthidalási logikát igényelne.

3. Mi történik, ha az EP1C4F400C8 meghibásodik a konfiguráció során?

Ha a konfiguráció meghibásodik, a Conf_Done PIN nem állítja magasot.Ez általában a bitstream fájl hibájára, a feszültségszekvenálásra vagy a PIN -beállításra mutat, és a tervezési folyamatban újra kell ellenőrizni.

4. Az EP1C4F400C8 interfész közvetlenül a DDR memóriával?

Számos I/O szabványt támogat, de nincs olyan natív DDR interfész, mint a modern FPGA.További tervezési megfontolásokra vagy áthidaló alkatrészekre lehet szükség.

5. Hogyan hasonlít az EP1C4F400C8 az újabb FPGA -khoz?

A modern eszközökhöz képest az EP1C4F400C8 alacsonyabb sebességgel, kevesebb logikai sűrűséggel és kevesebb fejlett funkcióval rendelkezik.Ez azonban továbbra is költséghatékony választás a stabil, középkategóriás terveknél, ahol az élvonalbeli teljesítmény nem szükséges.

EPM3256AFC256-7 CPLD áttekintés: Jellemzők, Pinout, Programming és Alkalmazások

2025/10/3 -en

ADG432BR Analóg kapcsoló IC: specifikációk, pinout, alternatívák és adatlap

2025/10/2 -en

Népszerű hozzászólások

-

Komplex utasítás beállított számítógépek: Hogyan változtatták meg a számítástechnikát?

8000/04/19 -en 147781

-

USB-C pinout és funkciók

2000/04/19 -en 112059

-

A Xilinx Unified Simulation Primitívumok használata: Átfogó útmutató az FPGA tervezéséhez és szimulációjához

1600/04/19 -en 111352

-

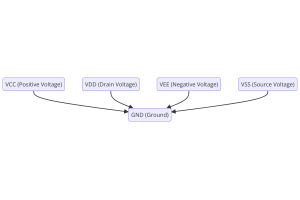

Tápfeszültségek az elektronikában: VCC, VDD, VEE, VSS és GND jelentése

0400/04/19 -en 83814

-

RJ45 Csatlakozó útmutató: Pinout, vezetékek, kábeltípusok és felhasználások

1970/01/1 -en 79628

-

A végső útmutató a vezetékes színkódokhoz a modern elektromos rendszerekben

Az, ahogyan az elektromos rendszereink a színeket használják, nem csak a megjelenéshez.Minden huzalszín most egy adott funkciót jelöl, megkönnyítve az elektromos alkatrészek azonosítását és kezelés...1970/01/1 -en 66998

-

Tisztító szelep útmutató: funkció, tünetek, tesztelés és a motor optimális teljesítményének cseréje

A tisztítószelep az autó rendszerének kulcsfontosságú része, amely segít a levegő tisztaságának megőrzésében az üzemanyag -gőzök kezelésével, mielőtt elmenekülhetnek a légkörbe.Ez nem csak a szenny...1970/01/1 -en 63120

-

Minőség (q) tényező: egyenletek és alkalmazások

A minőségi tényező, vagy a „Q” fontos, amikor ellenőrzi, hogy az induktorok és a rezonátorok hogyan működnek az elektronikus rendszerekben, amelyek rádiófrekvenciákat (RF) használnak.A 'Q' megméri,...1970/01/1 -en 63057

-

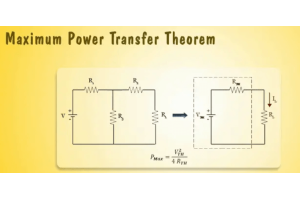

A csúcsteljesítmény elérése a maximális energiaátviteli tételgel

A maximális teljesítményátviteli tétel elmagyarázza, hogy a forrásból, például az akkumulátorból vagy a generátorból származó energia hogyan áramlik a csatlakoztatott terhelésbe.Megmutatja azt a po...1970/01/1 -en 54097

-

A23 akkumulátor specifikációi és kompatibilitása

Az A23 akkumulátor egy kicsi, hengeres alakú akkumulátor, nagy feszültséggel.A 23A, 23AE vagy MN21 néven is 12 voltos és sokkal magasabb, mint az AA vagy AAA akkumulátorok.Különleges kiala...1970/01/1 -en 52207